1. 서 론

2. 샘플 준비 및 분석 과정

3. 결 과

3.1 표면 재결합 특성 및 in-diffusion 도핑 농도 평가

3.2 PL 이미지를 통한 Jom 평가 결과

3.3 접촉 비저항 평가 결과 및 poly-Si 표면 손상 구조 관찰

4. 결 론

1. 서 론

스크린 프린팅을 통한 전극 형성 기술과 금속 페이스트의 발전은 태양전지 효율의 비약적인 발전을 일으킨 요소 중 하나이다. 지난 몇 년간의 이러한 발전으로 인해 PERC (passivated emitter rear cell), PERL (passivated emitter and rear locally diffused cell) 구조의 태양전지가 현재 산업에서 양산되고 있다. 최근에는 반송자 수명과, 선택성(carrier selectivity)이 높은 태양전지 구조로서 n-type 기반 TOPCon (tunnel oxide passivated contact) 태양전지가 각광을 받고 있고, 일부 업체에서는 이미 양산화하여 추가적인 효율 향상을 위한 지속적인 연구를 활발하게 진행하고 있다1-6). 이에 따라, TOPCon 구조에 대한 전극 형성 기술개발이 자연스럽게 관심을 받고 있다.

태양전지 후면에 적용되는 TOPCon 구조의 폴리실리콘(poly-Si) 은 일반적으로 100~250 nm 범위에서 형성되고 있다. 하지만, poly-Si 에서 발생하는 기생 흡수(parasitic absorption)로 인한 전류밀도 감소가, TOPCon 태양전지 효율 향상을 일부 상쇄하고 있다7-8). 기생 흡수를 감소시키기 위해서는 poly-Si 두께를 감소시켜야 하는데, 70 nm의 poly-Si를 사용한 문헌에 따르면 전극 재결합 전류밀도(Jom)가 1000 fA/cm2 까지 상승했다고 보고된다9). 따라서, 표면 패시베이션의 질과 전극의 ohmic contact 을 유지하는 것이 인쇄 전극형성의 관건이다. 이를 위해, paste 공급업체들은 이에 적합한 paste를 개발하기 위해 많은 노력을 하고 있고, 개발된 paste를 통해 최적화된 공정 조건을 확보하는 것도 매우 중요하다.

본 논문에서는, 인 도핑 된 poly-Si 두께와 인쇄 전극 소성 온도에 따른 전극재결합 전류밀도를 PL(photoluminescence) 이미징 기술을 통해 평가하였다. PL 이미징을 통해 Jom을 평가하면, 태양전지 양면에 전극을 형성할 필요가 없고, 전극면적비율(Fm)에 따른 개방전압(Voc)과 표면재결합 전류밀도(Jo)를 한 샘플에서 동시에 추출할 수 있는 장점이 있다. 또한, 전극의 ohmic contact 을 평가하기 위해 transfer length method (TLM) 방법을 통해 접촉비저항을 평가하였다. 이 실험을 통해, poly-Si 의 두께와 소성온도 조건이 TOPCon 태양전지의 전극재결합과 전기적 특성에 대해 이해할 수 있다.

2. 샘플 준비 및 분석 과정

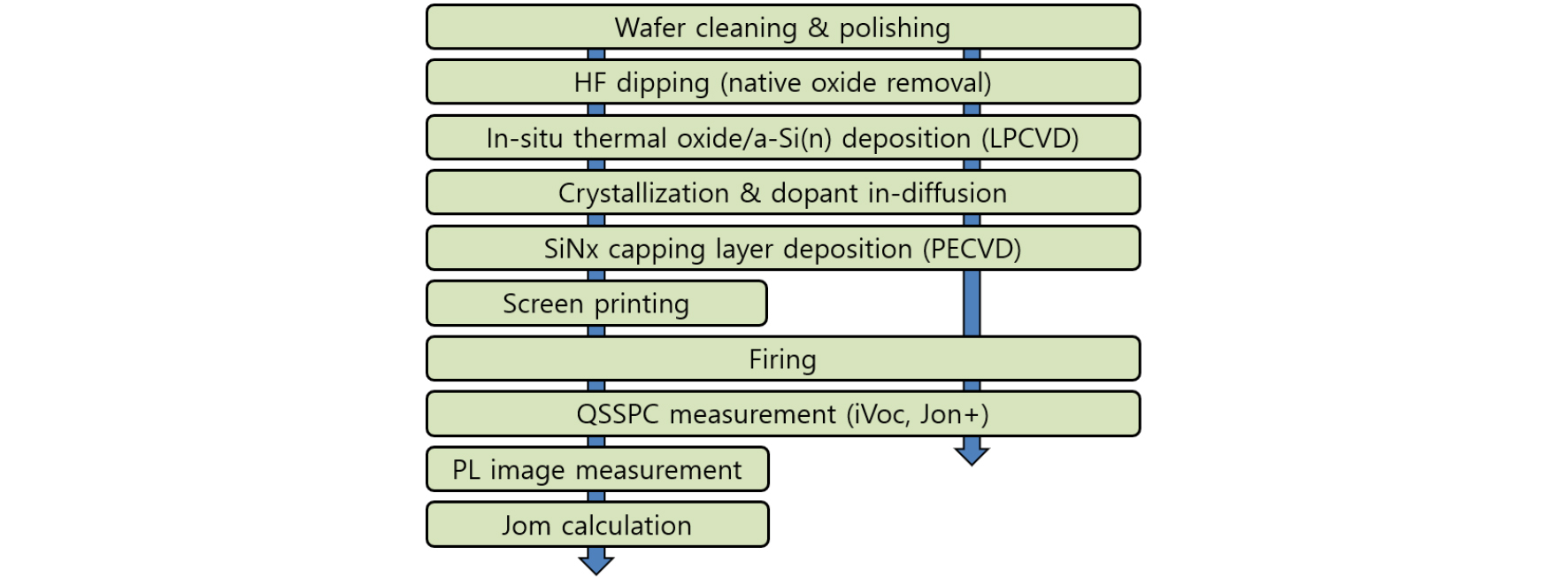

Jom 평가를 위한 샘플은 (100) 방향의 n형 실리콘 웨이퍼의 RCA cleaning과 KOH 용액을 통한 화학적 폴리슁(polishing)으로 시작되었다. 폴리슁 된 웨이퍼에 LPCVD를 통해 1.5 nm 두께의 실리콘 산화막(SiO2)과 인(phosphorous) 도핑 된 비정질 실리콘을 in-situ 방식으로 증착하였다. 비정질 실리콘을 poly-Si 으로 결정화하고, 기판 내부로 인을 in-diffusion 시키기 위해 tube furnace를 통해 925℃에서 30분 동안 열처리하였다. Poly-Si 위에 PECVD를 통해 실리콘 질화막(SiNx)이 80 nm 두께로 증착되었다.

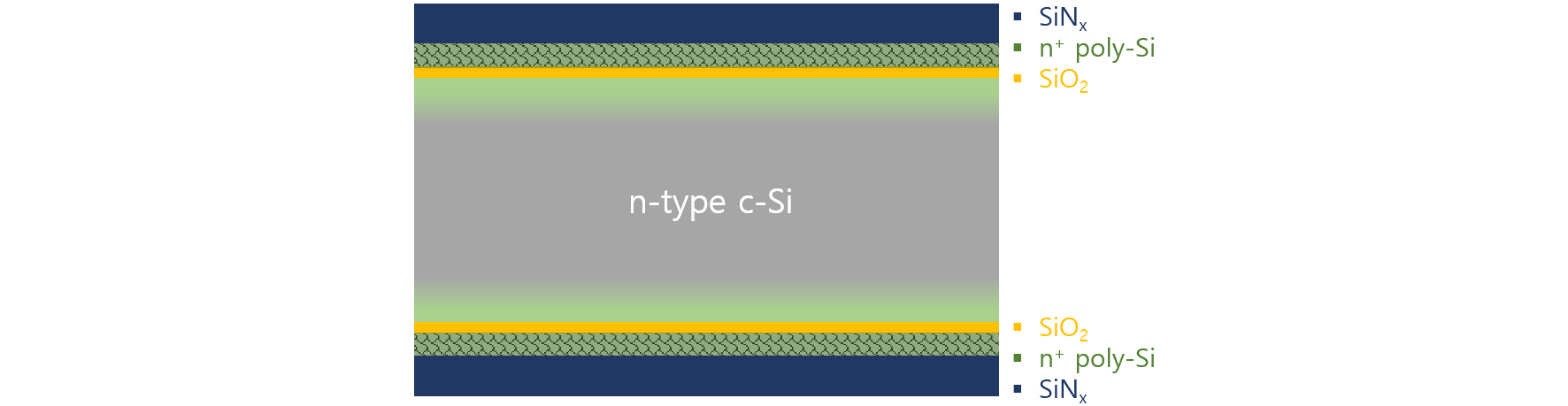

전극형성 전 샘플 구조는 Figure 1과 같이 양면 대칭으로 형성되었다. 이후, 샘플의 단면에 Ag paste를 스크린 프린팅 한 후, 건조(drying)와 소성(firing) 과정을 거쳐 전극을 형성하였다. 본 실험에서는 poly-Si 두께를 50 nm, 100 nm, 150 nm 세 조건으로 나누었고, 각 poly-Si 두께별 샘플은 730-880℃ 의 범위에서 30℃ 간격으로 소성 최고 온도를 가변하였다. 샘플 준비 과정은 Figure 2에 정리되었다.

Jom을 평가의 이론적 개념은 T. Fellmeth et al.에 의해 처음 제안되었다10). 제작된 대칭구조의 샘플의 단면에 형성된 금속전극의 면적 비율에 따른 태양전지 재결합 전류밀도(Jo1)는 식 (1)과 같이 표면재결합전류 밀도(Jos), Jom, base 영역(벌크+표면)재결합 전류밀도(Job)로 표현 된다. 식 (1)은 식 (2)로 정리될 수 있고, 이는 Jo1을 y축, Fm을 x축으로 하는 1차 함수로 표현된다. 이때, 이 함수의 기울기에 Jos를 더하여 Jom을 추출할 수 있다.

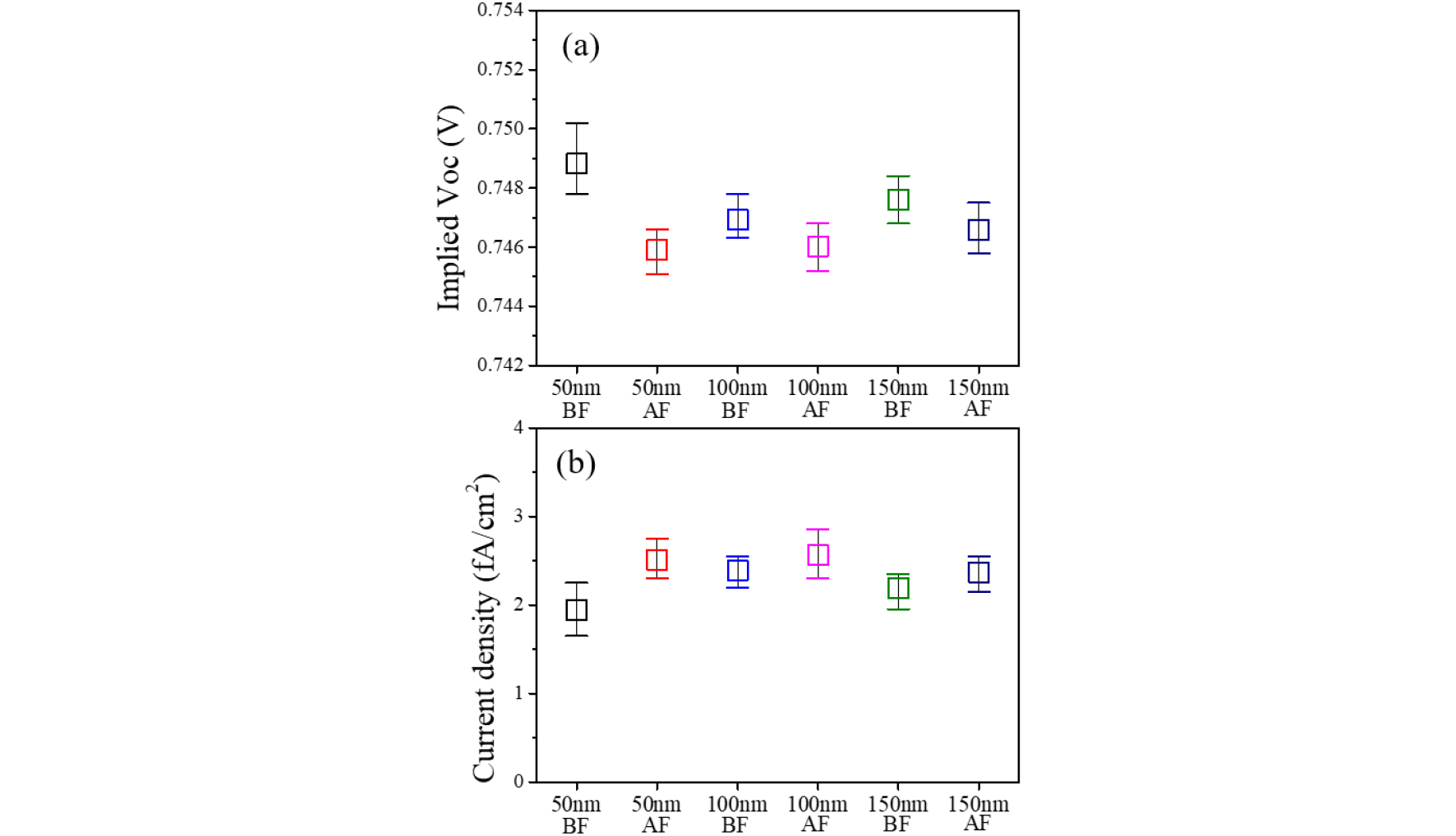

Jos는 Figure 3과 같이 금속전극이 형성되지 않은 중앙 영역에서 QSSPC (quasi-steady-state photoconductance, Sinton WCT-120) 측정을 통해 평가 되었다11). PL 이미징 장비(BT imaging, LIS-R3)를 통해 샘플의 implied Voc (iVoc) 이미지를 촬영한 후, iVoc를 식 (3)을 통해 Jo1을 계산하였다. 각 Fm에 대한 Jo1 값은 Figure 2의 그래프와 같이 선형 fitting 되었고, 얻어진 기울기를 통해 Jom이 계산되었다.

3. 결 과

3.1 표면 재결합 특성 및 in-diffusion 도핑 농도 평가

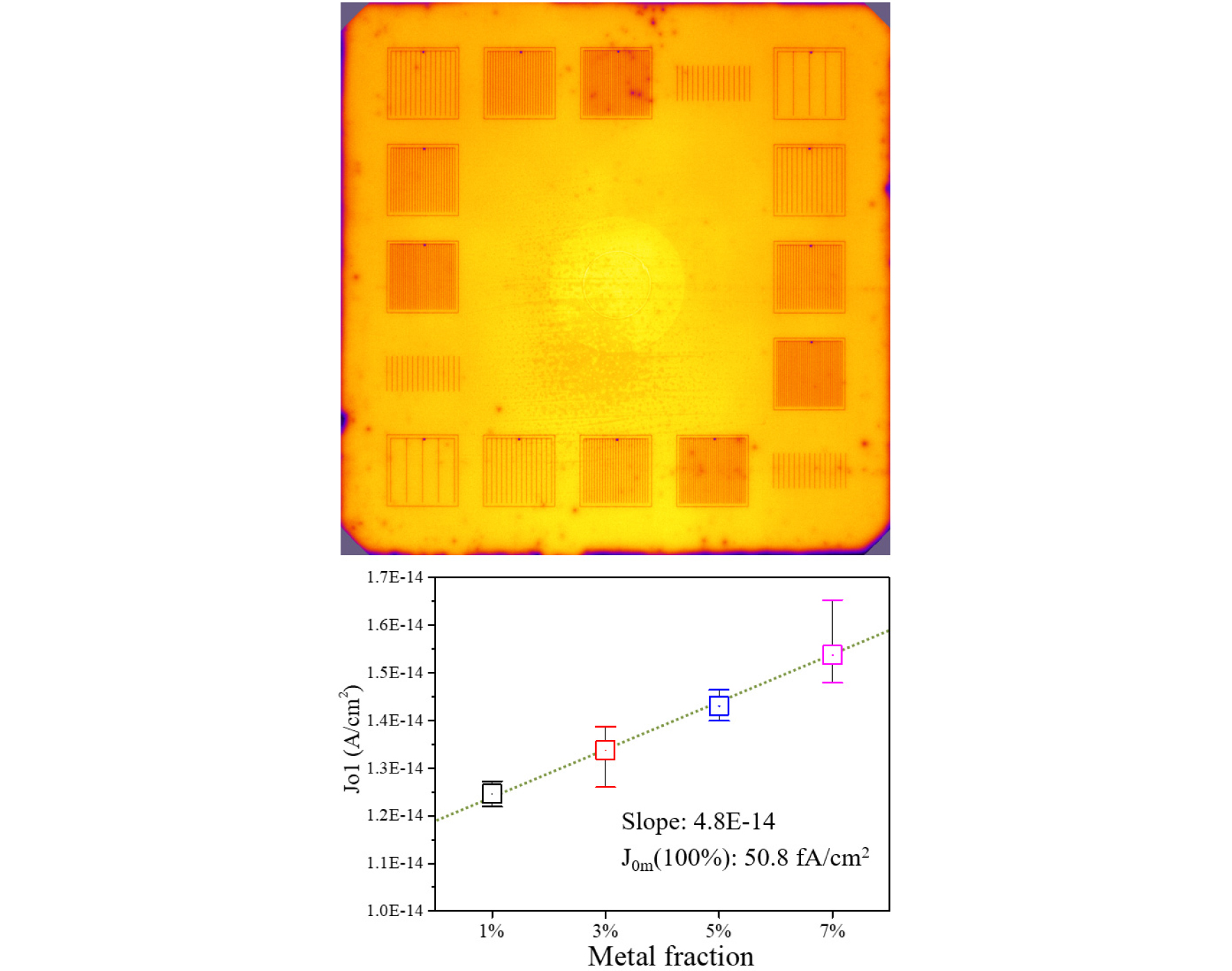

정확한 Jom을 평가하기 위해서는 정확한 표면재결합 전류밀도(Jos)를 측정하는 것이 필요하다. 소성 전/후 표면 passivation 의 변화를 파악하기 위해 소성 전 QSSPC 측정결과와 소성 최고온도 880℃에서 소성 후 QSSPC 측정결과를 통해 얻어진 단면 Jos와 iVoc 경향을 Figure 4 그래프로 나타내었다. 정리하였다. TOPCon 구조를 통한 단면 Jos는 poly-Si의 두께에 무관하게 평균 1.9~2.4 fA/cm2로 매우 높은 passivation 상태를 보였고, iVoc는 최대 748.8 mV를 보였다. 하지만, 소성 후 단면 Jos는 다소 상승하여 평균 2.5 fA/cm2 로 거의 일정하게 나타났다.

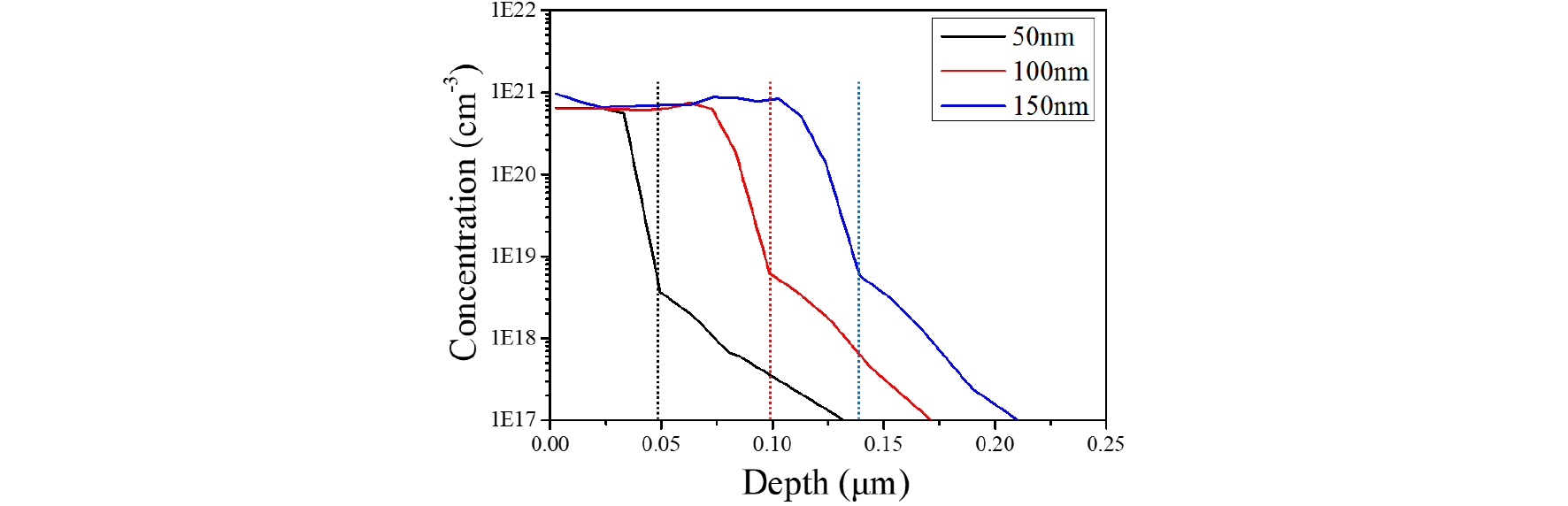

poly-Si 증착 두께 및 인(P) in-diffusion 농도를 파악하기 위해, ECV (electrochemical capacitance-voltage)를 측정했다. Figure 5는 각 poly-Si 두께에 따른 ECV 측정 결과로, 샘플 중앙에서 측정되었다. 50 nm, 100 nm 조건은 정확하게 증착되었고, 150 nm 목표 조건은 약 140 nm로 측정되었지만, 국부적인 균일도 차이로 인한 결과일 가능성이 있다. 실리콘 기판으로의 P in-diffusion 도핑 profile은 세 조건 모두 거의 동일한 결과를 보였다. 또한, poly-Si 두께에 무관하게 P 농도의 최대값도 거의 7~9×1020 cm-3 범위에서 무한 소스로서의 역할을 하는 것을 확인했다. 표면 재결합 전류밀도가 세 조건에서 유사한 이유도 이러한 도핑 profile에 따른 계면에서의 band bending과 Auger 재결합의 양이 유사하기 때문으로 판단된다.

3.2 PL 이미지를 통한 Jom 평가 결과

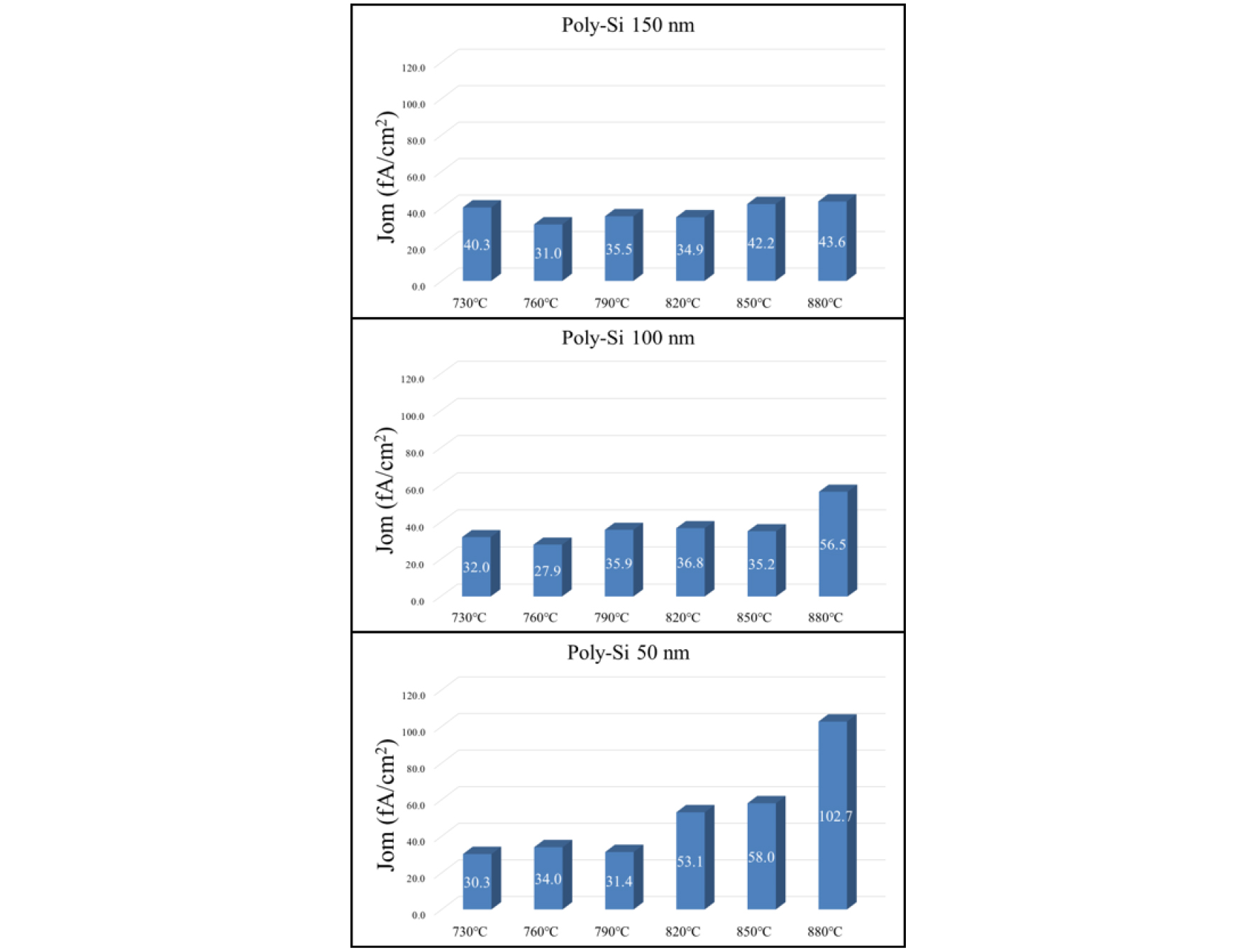

Figure 6은 poly-Si 두께 별로 소성 최대 온도를 가변하여 Jom을 평가한 결과이다. Poly-Si 두께 150 nm의 경우, 소성 온도 변화에 따른 Jom 이 약 30~40 fA/cm2 정도로, 온도가 상승함에 따라 Jom의 뚜렷한 증가가 없었다. 100 nm 조건에서는 850℃ 이상에서 Jom이 약 20 fA/cm2 정도 상승했고, 50 nm 조건은 820℃ 부터 Jom이 상승하기 시작해서 880℃에서는 약 103 fA/cm2 까지 상승했다.

소성 온도 상승에 따른 Jom 증가의 메카니즘은 금속 페이스트가 SiNx를 뚫고 poly-Si과 접촉하는 과정에서 발생하는 실리콘 기판 표면의 패시베이션 손상이다. Poly-Si 층이 두꺼울수록 아래의 SiOx 층까지 손상 받을 가능성이 적어진다. 하지만, poly-Si 층이 너무 두꺼우면 기생흡수가 많아져 전류밀도가 감소하므로 적절한 최적점을 찾는 것이 중요하다. 이러한 메커니즘에 의해 두꺼운 poly-Si 층의 경우, 소성 온도 증가에도 Jom이 쉽게 상승하지 않았다고 판단 할 수 있다. 50 nm poly-Si 두께의 경우, 880℃ 소성 조건에서 poly-Si 층 손상이 다른 조건에 비해 커졌을 것으로 예상할 수 있다.

3.3 접촉 비저항 평가 결과 및 poly-Si 표면 손상 구조 관찰

Poly-Si 두께와 소성 최대 온도에 따른 접촉 비저항은 Figure 3 PL 이미지 상에 보이는 TLM (transfer length method) 패턴을 통해 평가되었다. 접촉 비저항의 정확한 평가를 위해 TLM 패턴의 전극 양끝을 레이저로 절단하여 전극과 샘플의 폭을 1 cm 로 고정하였다.

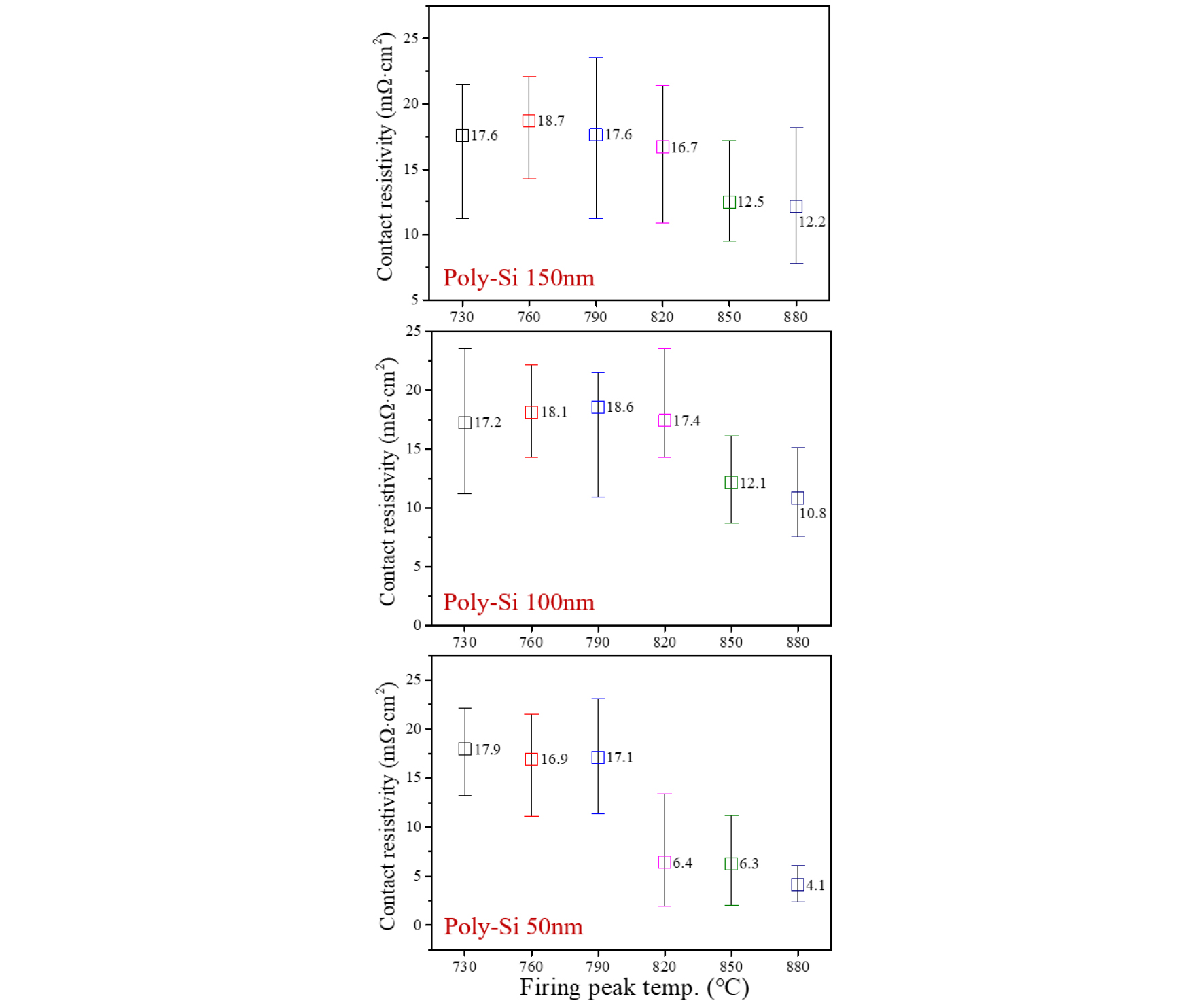

Figure 7은 poly-Si 두께와 소성 최대 온도에 따른 접촉 비저항을 오차 막대그래프로 나타낸 것이다. 모든 poly-Si 두께 조건에서 Jom이 30~40 fA/cm2 정도를 보였던 소성 온도에서는 약 17~19 mΩ・cm2로 평균 접촉 비저항이 매우 높았고, 오차 범위도 컸다. 소성온도가 820℃ 이상이 되면서 점차 접촉 비저항 값이 낮아 졌고, 오차 범위가 여전히 컸지만 poly-Si 50 nm 두께 조건에서는 최소 1.9 mΩ・cm2의 접촉비저항이 평가되었다. 이러한 오차범위는 poly-Si의 capping 층으로 사용된 SiNx 막의 증착온도가 500℃에서 이루어짐에 따라, 막의 밀도가 높아져 페이스트에 의해 쉽게 뚫리지 못한 것이 원인으로 판단된다.

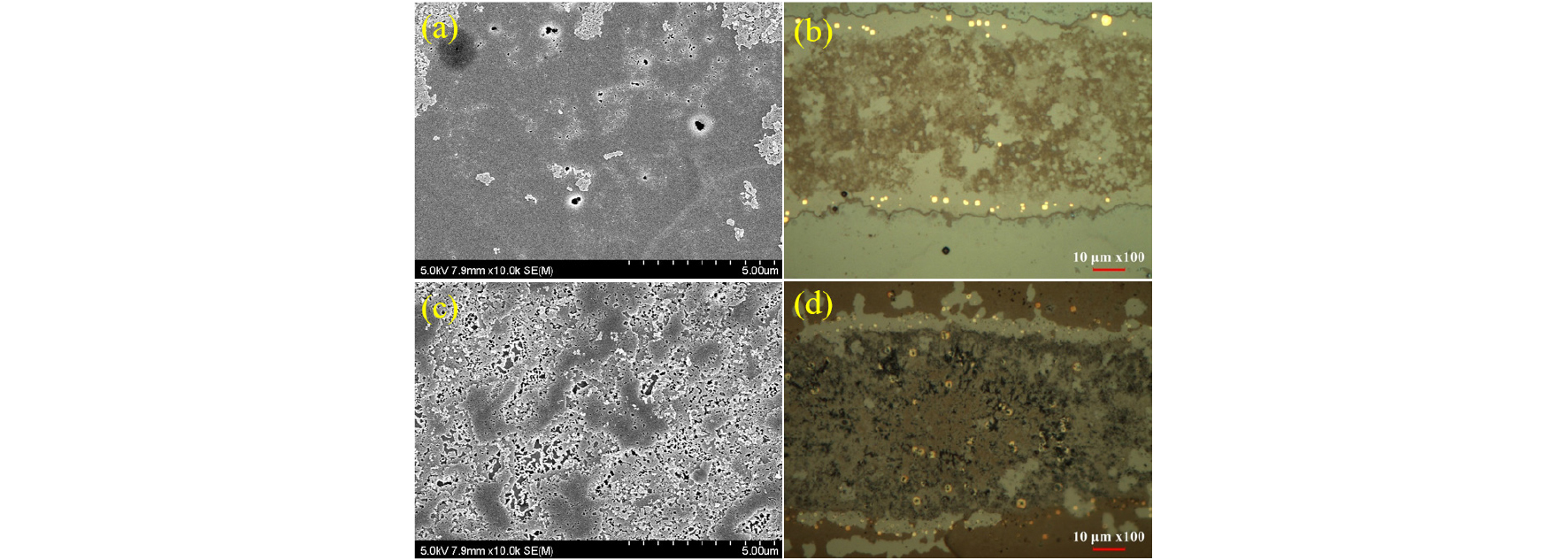

이를 확인하기 위해, FE-SEM (field emission scanning electron microscope) 및 OM (optical microscope)을 측정하였다. Figure 8은 poly-Si 50 nm 두께 조건에서 730℃, 880℃ 온도로 소성한 샘플을 전극과 유전막을 제거한 후, FE-SEM 및 OM을 통해 전극 영역의 표면을 관찰한 결과이다. 이미지를 통해 730℃에서 소성한 샘플의 전극 표면 구조를 관찰한 결과, OM 이미지의 갈색으로 보이는 전극 잔여물질 아래에 있는 회색 표면이 poly-Si 층으로 판단되었다. 이 영역을 FE-SEM 이미지로 확대해 보았을 때, poly-Si 층의 손상이 거의 없는 것을 확인할 수 있었다. 따라서, 820℃ 이하의 소성 최대온도에서는 SiNx capping 층의 에칭과정이 완전히 끝나지 않았거나, poly-Si 과 충분히 접촉하지 못한 것으로 판단할 수 있다.

반면, 880℃ 소성 샘플의 경우, OM 이미지 상에서도 poly-Si 층의 damage로 판단되는 표면 구조가 전극영역 전역에 거쳐 확인되었고, FE-SEM 이미지를 통해서도 poly-Si 층의 손상이 많이 발생한 것을 확인 할 수 있었다. 이와 같은 poly-Si 층 에칭은 다른 문헌에서도 확인할 수 있다12-13). SiNx 층의 증착 온도나 굴절률을 조절하여 에칭 속도를 증가 시킨다면, 더 낮은 온도에서도 전극형성이 가능할 것으로 판단된다. 이러한 방법을 통해 후면 TOPCon의 전극 소성 온도의 범위를 조절하면, 전면 전극의 소성 온도 범위와 호환이 잘 되도록 공정을 설계하는데 도움이 될 것으로 판단된다.

4. 결 론

본 논문에서는 TOPCon 구조의 poly-Si 두께와 소성온도에 따른 Jom을 PL 이미지를 통해 평가했고, TLM 방법을 통해 접촉 비저항도 평가했다. 실리콘 기판 양면에 형성된 TOPCon 구조의 패시베이션은 고온 소성 후에도 크게 변하지 않고 유지되는 것으로 확인되었다. Jom과 접촉 비저항 평가 결과, 특정 온도 이하에서는 전극 접촉이 제대로 되지 않아 Jom은 30~40 fA/cm2로 재결합이 매우 낮았지만, 평균 접촉 비저항이 약 17~19 mΩ・cm2로 전극 접촉이 잘 안된 것을 확인 할 수 있었다. Poly-Si 50 nm는 고온 소성 시 접촉 비저항이 가장 낮았지만, 동시에 Jom도 급격하게 증가해 기판의 손상도 있을 것으로 예상된다.

FE-SEM 및 OM을 통한 표면구조 분석결과, 820℃ 이하의 소성 최대 온도에서는 SiNx 의 에칭이 완료되지 않아 poly-Si 층의 손상이 거의 없었고, 소성 온도가 상승함에 따라 접촉 비저항이 점점 감소해서 최소 1.9 mΩ・cm2을 기록했다. 본 실험을 통해, SiNx의 밀도가 높은 경우 페이스트에 의한 에칭이 제한됨에 따라 전극접촉에 요구되는 소성온도가 증가할 수 있고, 접촉 비저항의 산포가 커짐을 확인했다. 실험 결과를 통해, 전면 전극과 호환되는 소성온도를 최적화하는 하나의 방법으로 사용될 수 있다고 판단된다.